嵌入式系统介绍

概述

本系列文章主要是重新整理 Embedded Systems-Shape The World 课程的相关学习笔记,另外会增加一些延伸的知识点或者资源材料等。

嵌入式系统和传统的计算机系统及其他复杂的大型系统相比,有很多不同的地方,至少在现代的电子系统爱好者看来,自己动手设计嵌入式系统要更加容易上手、更加富有乐趣,这也与嵌入式系统本身的特点有关。自底向上的学习方式有三个优势:首先是没有操作系统,因此几乎很容易理解所有的程序组件并且可以动手修改,相反,比如如果直接使用Linux内核,我们就不得不去理解复杂的进程管理、内存管理以及复杂的设备驱动框架等;第二,嵌入式系统包含真实世界环境的输入/输出而不是构建在大量抽象概念的系统上(当然抽象方法是构建大型系统的基本方法);最后,嵌入式系统遍布在各种产品中,我们随处可见也就随处可以学习。

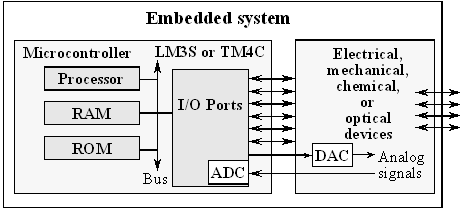

嵌入式系统的基本结构主要包括微控制器(Microcontroller)和与其交互的外部设备:

嵌入式系统的一个重要的特点是实时性(Real Time),它是指输入-处理-输出流程的时间延迟存在一个上限,这种响应时间(response time)也称为接口延迟(interface latency)。特别对于一些周期性任务,嵌入式系统保证在一个小的上限时间误差内执行连续的两次周期性任务。

嵌入式系统大多数是解决某个特定的问题或者实现特定的功能,这与通用计算机不同。嵌入式系统的开发调试过程也有些不同,如今在模拟的软硬件仿真环境中进行开发,最后再下载到实际硬件上测试的流程越来越重要。

I/O接口(I/O Interface)

I/O接口被定义为I/O端口、外部电路、硬件设备和软件的集合,它们组合起来使得计算机可以与外部世界通信。一般来说,我们可以将I/O接口分为四类:

- 并行接口(Parallel Interface)

- 串行接口(Serial Interface)

- 模拟接口(Analog Interface)

- 时钟接口(Time Interface)

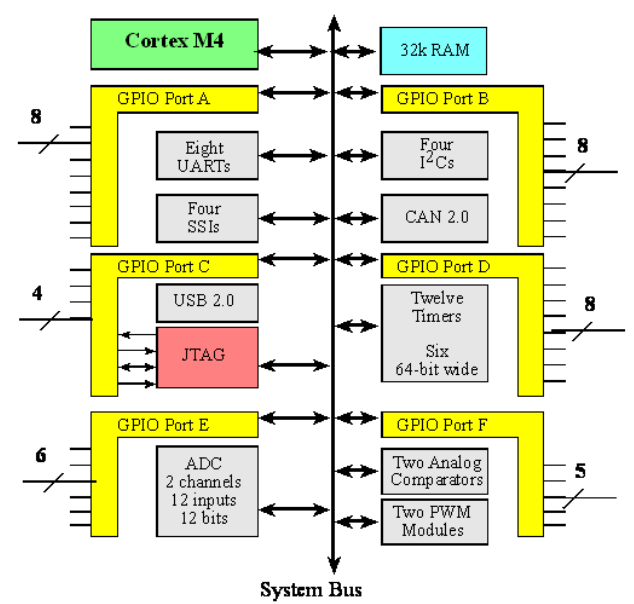

如TM4C123G微控制器的架构如下:

设备驱动(Device Driver)

设备驱动是一种中间层的角色,它对下直接与底层硬件通信,按照设备具体的工作方法,读写设备寄存器,处理轮询、中断和DMA,以及内存映射等;对上则提供更加抽象的API接口,使得上层软件开发者从过多的硬件细节中解脱出来,更重要的是,这也体现了一种分层设计的思想。设备驱动不依赖操作系统的存在,在某些应用场景可直接由应用层调用。

地址空间

嵌入式微处理器可以有更直接的的地址空间布局,相反,如果支持操作系统的MMU,这种布局相对来说就不那么直接了,如果再引入用户空间和内核空间的区分,那么它的结构就会变得更加复杂。

并行IO端口(GPIO)

GPIO是最简单的IO端口,它可以分为输入端口和输出端口。在大多数微控制器上,每一个GPIO端口都可以被软件配置为输入和输出,这是通过组合触发器和三态门来实现的。对于大多数微控制器来说,都使用内存映射来访问IO端口,即通过一个内存地址来读或者写某个IO端口,但它和访问真正的内存并不完全相同。IO端口被映射的内存区域有着特殊的限制,有些bit位只能读或者只能写,或者不能被修改,或者只能被设置等。以TM4C123G为例,它提供方向寄存器(GPIO_PORTX_DIR_R)来设置端口是输入还是输出端口;提供数据寄存器(GPIO_PORTX_DATA_R)来进行实际的输入输出访问,而这些宏实际对应的都是一个特定的内存地址。另外,微控制器还会复用某些pin口来执行不同的功能,如支持串口、ADC等,这同样是通过设置特定的控制寄存器(对应一个内存地址)来完成的。

并口大都只适合近距离通信。

串口通信

UART是全双工串口通信,RXd/TXd分别用来传输数据和接收数据。通信协议相对简单,在有效数据位上增加起始位、停止位以及可选的校验位,同时在结构上还包括FIFO和移位寄存器。UART之所以称为异步通信,是它的通信双方只需要保持波特率的一致,各自的时钟频率可以不同(但差异要保持在5%以内)。相对UART的异步特征,SSI(或SPI)则提供同步通信,即通信双方之间的连接线包括同步时钟线。

异步通信:

同步通信:

忙等、轮询和中断

在不同的场景使用要不同的策略。中断策略适合与IO设备复杂多样、延迟时间不确定的场景;忙等(Busy-Wait)适合延时相对确定,IO设备简单的场景。

Systick定时器

Systick是一个计数器可以实现定时延迟或者周期性的中断。在TM4C123G上,同样是通过访问特定寄存器来对其进行配置和控制。Systick还可以用来实现调试功能,测试代码执行时间等。

Systick周期性中断适合于无法直接生成中断请求的IO设备或者需要并发执行IO操作的设备。

Phase-Lock-Loop(PLL)

PLL可以实现对系统运行时钟更好的控制,可以用来平衡功耗和性能;另外它也可以提供更精确的系统时间。PLL利用反馈原理,来实现稳定的高频信号。PLL通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成。